# Freescale Semiconductor Technical Data

MC100ES6056 Rev 4, 06/2005

# 2.5 V/3.3 V ECL/PECL/LVDS Dual Differential 2:1 Multiplexer

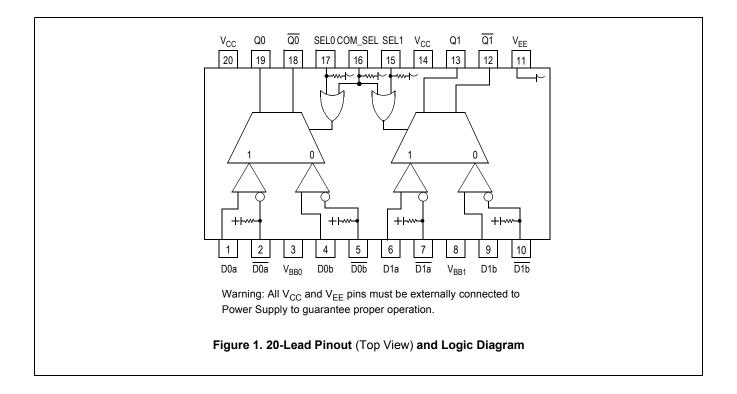

The MC100ES6056 is a dual, fully differential 2:1 multiplexer. The differential data path makes the device ideal for multiplexing low skew clock or other skew sensitive signals. Multiple  $V_{BB}$  pins are provided.

The V<sub>BB</sub> pin, an internally generated voltage supply, is available to this device only. For single-ended input conditions, the unused differential input is connected to V<sub>BB</sub> as a switching reference voltage. V<sub>BB</sub> may also rebias AC coupled inputs. When used, decouple V<sub>BB</sub> and V<sub>CC</sub> via a 0.01  $\mu$ F capacitor and limit current sourcing or sinking to 0.5 mA. When not used, V<sub>BB</sub> should be left open.

The device features both individual and common select inputs to address both data path and random logic applications.

The 100ES Series contains temperature compensation.

#### Features

- 360 ps Typical Propagation Delays

- Maximum Frequency > 3 GHz Typical

- PECL Mode Operating Range:  $V_{CC}$  = 2.375 V to 3.8 V with  $V_{EE}$  = 0 V

- ECL Mode Operating Range: V<sub>CC</sub> = 0 V with V<sub>EE</sub> = -2.375 V to -3.8 V

- Open Input Default State

- Separate and Common Select

- Q Output Will Default LOW with Inputs Open or at V<sub>EE</sub>

- V<sub>BB</sub> Outputs

- LVDS Input Compatible

- 20-Lead Pb-Free Package Available

| ORDERING INFORMATION |                    |  |  |  |  |  |

|----------------------|--------------------|--|--|--|--|--|

| Device               | Package            |  |  |  |  |  |

| MC100ES6056DT        | TSSOP-20           |  |  |  |  |  |

| MC100ES6056DTR2      | TSSOP-20           |  |  |  |  |  |

| MC100ES6056EJ        | TSSOP-20 (Pb-Free) |  |  |  |  |  |

| MC100ES6056EJR2      | TSSOP-20 (Pb-Free) |  |  |  |  |  |

© Freescale Semiconductor, Inc., 2005. All rights reserved.

#### Table 1. Pin Description

| Pin                             | Function                 |

|---------------------------------|--------------------------|

| D0a* – D1a*                     | ECL Input Data a         |

| D0a* – D1a*                     | ECL Input Data a Invert  |

| D0b* – D1b*                     | ECL Input Data b         |

| D0b* - D1b*                     | ECL Input Data b Invert  |

| SEL0* – SEL1*                   | ECL Indiv. Select Input  |

| COM_SEL*                        | ECL Common Select Input  |

| $V_{BB0}, V_{BB1}$              | Output Reference Voltage |

| Q0 – Q1                         | ECL True Outputs         |

| $\overline{Q0} - \overline{Q1}$ | ECL Inverted Outputs     |

| V <sub>CC</sub>                 | Positive Supply          |

| V <sub>EE</sub>                 | Negative Supply          |

## Table 2. Function Table

| SEL0 | SEL1 | COM_SEL | Q0, <mark>Q0</mark> | Q1, <mark>Q1</mark> |

|------|------|---------|---------------------|---------------------|

| Х    | Х    | Н       | а                   | а                   |

| L    | L    | L       | b                   | b                   |

| L    | Н    | L       | b                   | а                   |

| Н    | Н    | L       | а                   | а                   |

| Н    | L    | L       | а                   | b                   |

\* Input function will default LOW when left open.

## Table 3. General Specifications

|                                             | Value                                                     |                             |  |  |

|---------------------------------------------|-----------------------------------------------------------|-----------------------------|--|--|

| Internal Input Pulldown Resistor            | nternal Input Pulldown Resistor                           |                             |  |  |

| Internal Input Pullup Resistor              | Internal Input Pullup Resistor                            |                             |  |  |

| ESD Protection                              | Human Body Model<br>Machine Model<br>Charged Device Model | > 4 kV<br>> 400 V<br>> 2 kV |  |  |

| Thermal Resistance<br>(Junction-to-Ambient) | 0 LFPM, 20 TSSOP<br>500 LFPM, 20 TSSOP                    | 140°C/W<br>100°C/W          |  |  |

Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test

## Table 4. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol              | Characteristic                      | Conditions                                           | Rating                                         | Units    |

|---------------------|-------------------------------------|------------------------------------------------------|------------------------------------------------|----------|

| V <sub>SUPPLY</sub> | Power Supply Voltage                | Difference between V <sub>CC</sub> & V <sub>EE</sub> | 3.9                                            | V        |

| V <sub>IN</sub>     | Input Voltage                       | $V_{CC} - V_{EE} \le 3.6 \text{ V}$                  | V <sub>CC</sub> + 0.3<br>V <sub>EE</sub> – 0.3 | V        |

| I <sub>OUT</sub>    | Output Current                      | Continuous<br>Surge                                  | 50<br>100                                      | mA<br>mA |

| I <sub>BB</sub>     | V <sub>BB</sub> Sink/Source Current |                                                      | ±0.5                                           | °C       |

| T <sub>A</sub>      | Operating Temperature Range         |                                                      | -40 to +85                                     | °C       |

| T <sub>STG</sub>    | Storage Temperature Range           |                                                      | -65 to +150                                    | °C       |

1. Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

| Symbol           | Characteristics                                 | –40°C                 |                       |                       | 0°C to 85°C           |                       |                       | Unit |

|------------------|-------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|------|

| Symbol           | Characteristics                                 | Min                   | Тур                   | Max                   | Min                   | Тур                   | Max                   | Unit |

| I <sub>EE</sub>  | Power Supply Current                            |                       | 30                    | 60                    |                       | 30                    | 60                    | mA   |

| V <sub>OH</sub>  | Output HIGH Voltage <sup>(1)</sup>              | V <sub>CC</sub> -1085 | V <sub>CC</sub> -960  | V <sub>CC</sub> -880  | V <sub>CC</sub> -1025 | V <sub>CC</sub> -930  | V <sub>CC</sub> -860  | mV   |

| V <sub>OL</sub>  | Output LOW Voltage <sup>(1)</sup>               | V <sub>CC</sub> -1950 | V <sub>CC</sub> -1695 | V <sub>CC</sub> -1500 | V <sub>CC</sub> -1950 | V <sub>CC</sub> -1705 | V <sub>CC</sub> -1500 | mV   |

| V <sub>IH</sub>  | Input HIGH Voltage                              | V <sub>CC</sub> -1165 |                       | V <sub>CC</sub> -880  | V <sub>CC</sub> -1165 |                       | V <sub>CC</sub> -880  | mV   |

| V <sub>IL</sub>  | Input LOW Voltage                               | V <sub>CC</sub> -1810 |                       | V <sub>CC</sub> -1475 | V <sub>CC</sub> -1810 |                       | V <sub>CC</sub> -1475 | mV   |

| V <sub>BB</sub>  | Output Reference Voltage                        | V <sub>CC</sub> -1380 | V <sub>CC</sub> -1290 | V <sub>CC</sub> -1220 | V <sub>CC</sub> -1380 | V <sub>CC</sub> -1290 | V <sub>CC</sub> -1200 | mV   |

| V <sub>PP</sub>  | Differential Input Voltage <sup>(2)</sup>       | 0.15                  |                       | 1.3                   | 0.15                  |                       | 1.3                   | V    |

| V <sub>CMR</sub> | Differential Cross Point Voltage <sup>(3)</sup> | V <sub>CC</sub> –2.3  |                       | V <sub>CC</sub> -0.8  | V <sub>CC</sub> –2.3  |                       | V <sub>CC</sub> -0.8  | V    |

| I <sub>IH</sub>  | Input HIGH Current                              |                       |                       | 150                   |                       |                       | 150                   | μA   |

| IIL              | Input LOW Current                               | 0.5                   |                       |                       | 0.5                   |                       |                       | μA   |

1. Output termination voltage  $V_{TT}$  = 0 V for  $V_{CC}$  = 2.5 V operation is supported but the power consumption of the device will increase.

2. V<sub>PP</sub> (DC) is the minimum differential input voltage swing required to maintain device functionality.

3.  $V_{CMR}$  (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the  $V_{CMR}$  (DC) range and the input swing lies within the  $V_{PP}$  (DC) specification.

Table 6. AC Characteristics (V<sub>CC</sub> = 0 V; V<sub>EE</sub> =  $-2.5 V \pm 5\%$  or -3.8 V to -3.135 V; V<sub>CC</sub> =  $2.5 V \pm 5\%$  or 3.135 V to 3.8 V; V<sub>EE</sub> = 0 V)<sup>(1)</sup>

|                                     |                                          |                                                           | _                    | 40°C to 85°0      | 0                    |                |

|-------------------------------------|------------------------------------------|-----------------------------------------------------------|----------------------|-------------------|----------------------|----------------|

| Symbol                              | Characteristics                          |                                                           | Min                  | Тур               | Max                  | Unit           |

| f <sub>max</sub>                    | Maximum Frequency                        |                                                           |                      | > 3               |                      | GHz            |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation Delay to Output Differential | D to Q, <u>Q</u><br>SEL to Q, <u>Q</u><br>COM_SEL to Q, Q | 300<br>300<br>300    | 400<br>430<br>490 | 500<br>600<br>650    | ps<br>ps<br>ps |

| t <sub>SKEW</sub>                   | Skew                                     | Output-to-Output <sup>(2)</sup><br>Part-to-Part           |                      | 10                | 50<br>200            | ps<br>ps       |

| t <sub>JITTER</sub>                 | Cycle-to-Cycle Jitter                    | RMS (1σ)                                                  |                      |                   | 1                    | ps             |

| V <sub>PP</sub>                     | Minimum Input Swing                      |                                                           | 200                  | 800               | 1200                 | mV             |

| V <sub>CMR</sub>                    | Differential Cross Point Voltage         |                                                           | V <sub>CC</sub> -2.1 |                   | V <sub>CC</sub> -1.1 | V              |

| t <sub>r</sub> / t <sub>f</sub>     | Output Rise/Fall Time (20%–80%)          |                                                           | 70                   | 120               | 230                  | ps             |

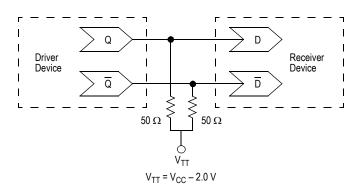

1. Measured using a 750 mV source, 50% duty cycle clock source. All loading with 50 $\Omega$  to V<sub>CC</sub>–2.0 V.

2. Skew is measured between outputs under identical transitions. Duty cycle skew is defined only for differential operation when the delays are measured from the cross point of the inputs to the cross point of the outputs.

Figure 2. Typical Termination for Output Driver and Device Evaluation

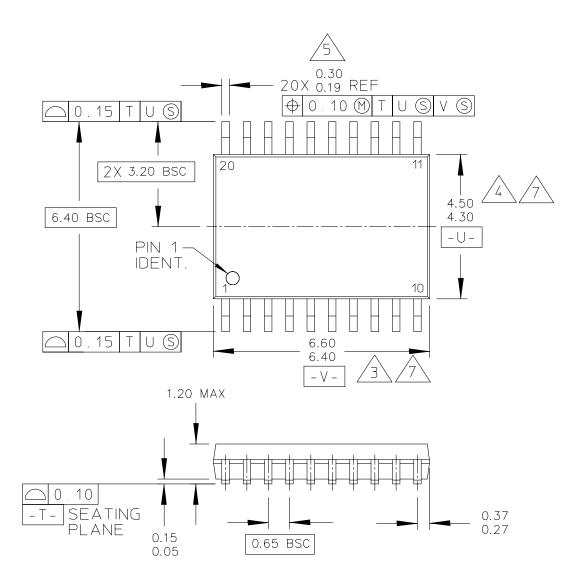

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. |                           | MECHANICAL OUTLINE |             | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|---------------------------|--------------------|-------------|----------------------------|-------------|

| TITLE:                                                  |                           |                    | DOCUMENT NO | : 98ASH70169A              | RE∨: B      |

|                                                         | 20 LD TSSOP, PITCH 0.65MM |                    | CASE NUMBER | : 948E-03                  | 09 MAR 2005 |

|                                                         |                           | STANDARD: JE       | DEC         |                            |             |

PAGE 1 OF 3

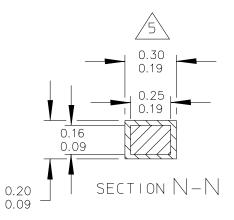

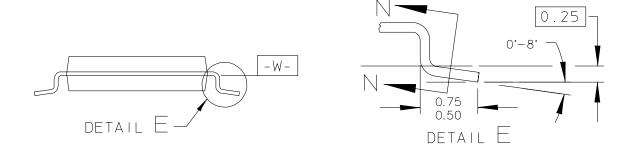

## CASE 948E-03 ISSUE B 20-LEAD TSSOP PACKAGE

# PACKAGE DIMENSIONS

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved. |                           | L OUTLINE    | PRINT VERSION NE | IT TO SCALE |

|---------------------------------------------------------|---------------------------|--------------|------------------|-------------|

| TITLE:                                                  |                           | DOCUMENT NE  | ]: 98ASH70169A   | RE∨: B      |

| 20 LD TSSOP, PITC                                       | 20 LD TSSOP, PITCH 0.65MM |              | 948E-03          | 09 MAR 2005 |

|                                                         |                           | STANDARD: JE | DEC              |             |

PAGE 2 OF 3

## CASE 948E-03 ISSUE B 20-LEAD TSSOP PACKAGE

NOTES:

- 1. CONTROLLING DIMENSION: MILLIMETER

- 2. DIMENSIONS AND TOLERANCES PER ANSI Y14.5M-1982.

- 3 DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE.

- DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 5 DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 6. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

/7 dimensions are to be determined at datum plane [-w-]

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved. MECHANICA |              | L OUTLINE | PRINT VERSION NE | JT TO SCALE  |               |             |

|-------------------------------------------------------------------|--------------|-----------|------------------|--------------|---------------|-------------|

| TITLE:                                                            |              |           |                  | DOCUMENT NO  | : 98ASH70169A | RE∨: B      |

|                                                                   | 20 LD TSSOP, | PITCH     | 0.65MM           | CASE NUMBER  | 948E-03       | 09 MAR 2005 |

|                                                                   |              |           |                  | STANDARD: JE | DEC           |             |

PAGE 3 OF 3

#### CASE 948E-03 ISSUE B 20-LEAD TSSOP PACKAGE

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005. All rights reserved.

MC100ES6056 Rev. 4 06/2005